# Design and implementation of the SMPS for IGBT Driver

<sup>1</sup>Hardik Khambhadiya and <sup>2</sup>Prof. P.N.Kapil <sup>1</sup>PG Scholar and <sup>2</sup>Assistant Professor, <sup>1,2</sup>Electrical Department, Institute of Technology, Nirma University, Ahmedabad, India

Abstract— Nowadays, MOSFET and Insulated Gate Bipolar Transistor (IGBT) drives supplies are a great source of interest because of requirement of medium power & high power drives. IGBT requires a highly sophisticated driver-card for the operation. Driver-card is a combination of DC-DC converter and driver IC. In this paper, design and implementation of the DC-DC converter is presented. This design provides isolated positive and negative voltage DC-rails required for IGBT gate drivers from a single 12V DC input supply. All this features comes with the consideration of minimal cost.

Keywords-converter, driver, Push-Pull, SG3525, SMPS

# I. INTRODUCTION

The majority of industrial devices mainly use a three-phase power supply for their operation and for the controlling purpose, there phase converter is required. The converter is made of various configuration of IGBT's. High-Power IGBTs require isolated gate drivers to control their operations. Isolated gate driver require isolated power supply for their operation. The emitter of the top IGBT floats, which require an isolated gate-driver. To reduce conduction losses, the gate pulses of the IGBTs are supplied with a much higher voltage than the actual gate-threshold voltages. Typically, 15 V to 18 V is applied at the gate to reduce Vce(on). When an IGBT is turned on, some voltage spikes are generated on the gate terminal because of the high inductances of wire, due to the high dv/dt and parasitic capacitance between the gate and emitter. The voltage spiked can cause a false turn-on for the bottom IGBT. A negative voltage at the gate helps to avoid this false turn-on trigger. Generally 15 V is applied to the gate for turn-on and -5 V is applied for turn-off the IGBT.

This design is intended to operate with a pre-filtered and regulated 12V input. The open-loop, free-running oscillator of the PWM controller (SG3525) can be used, SG3525 is Push-Pull PWM controller IC. This push-pull topology allows for more efficient use of the transformer core than the flyback or forward converters. Advantage of using push-pull topology is that multiple transformers can be connected in parallel to generate the voltage rails. The main purpose of designing a SMPS is to provide gate power supply to the driver circuit. SMPS converters the input 12V dc supply into 15V & -5V dc for the positive & negative driving of the IGBT respectively

#### **II. SMPS DESIGN**

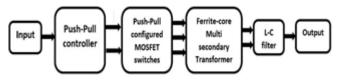

The Push-Pull configuration is normally used for output powers in the range of 100 to 500W. This topology is highly suited for this driver design because it gives compact design of transformer & filter, Very low output ripple and suitable for multiple output. Fig.2 shows block diagram of SMPS.

IJTRD|Mar-Apr2015 AvailableOnline@www.ijtrd.com

Fig.1 Block diagram of SMPS

#### **III. MAGNETICS COMPONENTS DESIGN**

# **Turns Calculation for High-Frequency Transformer:**

Specification of DC-DC converter:

Input voltage (nominal): 12V Output voltage: (1)15V, (2)5V Output current: 4A Switching frequency: 20 KHz

Calculating the number of required primary turns is:

$$N_{pri} = \frac{V_{in(nom)} * 10^8}{4 * f * B_{max} * A_c}$$

"ETD-39" ferrite is selected  $B_{max} = 2000$   $A_c = 1.25$ Primary turns:

$$N_{pri} = \frac{12 * 10^8}{4 * 20000 * 2000 * 1.25} = 6$$

To find secondary turns, voltage ratio has to be calculated:  $V_{min} = 12V$

Duty cycle = 90%Voltage to Transformer is: 0.90 \* 12 = 10.8V

Voltage ratio (secondary: primary) =  $\frac{15}{10.8}$  = 1.39  $N_{\text{sec}}$  = turn ratio \*  $N_{pri}$

$$\therefore N_{\text{sec}} = 1.39 * 6 = 8.34$$

Round off to the nearest number.  $N_{\text{sec}}$  = 9 turns

1. For the other secondary winding,

Voltage ratio (Secondary: primary)  $=\frac{5}{10.8}=0.46$

$$N_{\text{sec}} = turn \ ratio * N_{pri}$$

$$\therefore \ N_{\text{sec}} = 0.46 * 6 = 2.8$$

# Round off to the nearest number. $N_{sec}$ (2) = 3 turns

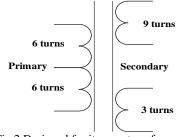

Designed transformer is as shown in Fig.2

Fig.2 Designed ferrite core transformer

#### Wire Gauge Selection:

The RMS values of the currents are given by:

$$I_{sec} = I_o * \sqrt{\frac{D_{max}}{2}}$$

As far as SG3525 controller is concern,  $D_{max} = 0.95$

$$\therefore I_{sec} = 4 * \sqrt{\frac{0.95}{2}} = 2.76A$$

Primary winding current:

$$I_{pri} = nI_{sec} \mathbb{I}_{1} + nI_{sec} \mathbb{I}_{2}$$

$\therefore I_{pri} = 1.39 * 2.76 + 0.46 * 2.76$

$\therefore I_{pri} = 5.1A$

The cross sectional areas can now be calculated by:

Current density is taken as 3 for unenforced air-cooled system.

$$a_{pri} = \frac{I_{pri}}{J} = \frac{5.1}{3} = 1.7 \ mm^2$$

$$a_{sec} = \frac{I_{sec}}{J} = \frac{2.76}{3} = 0.92 \ mm^2$$

#### **Cross check:**

Check for in equality,

$$A_w K_w \geq \sum_{i=1}^m a_i N_i$$

Using the actual values of the cross section area,

$$2(a_{pri}N_{pri}) + 2(a_{sec(1)}N_{sec(1)}) + 2(a_{sec(2)}N_{sec(2)})$$

$$\therefore 2(1.7*6) + 2(0.92*9) + 2(0.92*3) = 42.48 \ mm^2$$

From the datasheet of ETD-39 core, value of

Window area  $A_w = 178 \ mm^2$

Window factor taken as  $K_w = 0.4$

$$A_w K_w = 0.4 * 178 = 71.2 \, mm^2$$

ETD-39 core transformer is suitable for the proposed SMPS design.

# **Output Inductor Calculation for Push-Pull converter:**

$$L_{min} = \frac{[V_{in(max)} - V_{out}] \times T_{off(est)}}{1.4 \times I_{out(min)}}$$

Where:

$V_{\text{in}(\text{max})}\!=\!$  highest peak voltage following the output rectifier of that particular output.

$V_{out} = output voltage.$

$T_{\text{off(est)}} = \text{estimated}$  on time of power switches at the highest input voltage.

$I_{out}(min) = lightest$  expected load current for that output.

(1)For positive Side (+15V):

$$L_{min} = \frac{[16.3 - 15] \times 50 \times 10^{-6}}{1.4 \times 0.25}$$

$$L_{min} = 182 \,\mu H$$

(2)For negative side (-5V):

$$L_{min} = \frac{[6.3 - 5] \times 50 \times 10^{-6}}{1.4 \times 0.25}$$

$$L_{min} = 182 \,\mu H$$

# **Output Inductor turn Calculation:**

Selected ferrite core: Ring (R-12,5),  $AL = 2200 nH/N^2$

$$N = \sqrt{\frac{L}{AL}}$$

Where:

N=Number of turns L=Required value of inductance AL=Effective permeability

$$T = \sqrt{\frac{182000}{2200}}$$

$$N = 9$$

Ν

### **IV. SG3525 CONTROLLER**

There are numerous PWM controllers available that make the use and application of PWM very easy. One of the most popular of such controllers is the versatile and ubiquitous SG3525.SG3525 is widely used in DC-DC converters (buck, boost), AC-DC converter, and DC-AC inverters. Values of Rt(timing resistor) & Ct(timing capacitor) is selected in a such a way that, SMPS circuitry works at switching frequency of 20 KHz.

$$f = \frac{1}{Ct(0.7 * Rt + 3RD)}$$

Select the values of Rt, Ct and RD in such a way that, it will result f = 40 KHz

IJTRD|Mar-Apr2015 AvailableOnline@www.ijtrd.com

$$\therefore f = \frac{1}{10^{-9} * (0.7 * 35000 + 3 * 10)} = 40766 \, Hz$$

For the Push-Push configuration of the SMPS. As the oscillator frequency is 40706 kHz, the switching frequency will be the half of the oscillator frequency.

### 0.5 \* 40766 = **20 KHz**

Values of frequency components of SG3525:

Rt = 35000 ΩCt = 1 nF (102) RD = 10 Ω

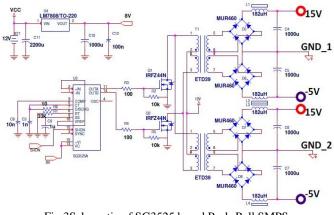

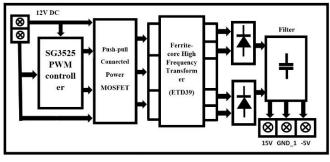

Fig.3Schematic of SG3525 based Push-Pull SMPS

In fig.3 SG3525 PWM controller is shown which is used to generate two complementary pulses which is directly given to the power MOSFET (IFRZ44N). This Push-Pull configuration drive primary winding of two ETD-39 ferrite core high frequency transformer. For doing this, transformer primary has to be connected in parallel. Centre-taped end is connected to +VCC (12V) input driver supply while another two terminals of the transformer is driven by push-pull configured power MOSFET.For the rectification purpose, MUR460 ultrafast recovery diode is used to rectify the 20 kHz AC into DC. Capacitor 1000uf, 25v is sufficient enough to filter-out dc waveforms of 40 kHz. At the end of the power supply, a pair of dual voltage are ready to powering the driver circuitry. Fig.4 shows top-view of the designed SMPS.

Fig.4 Top-view of designed SMPS

### V. Hardware Results

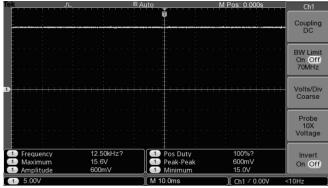

(1)Voltage Waveform Captured at positive 15V side in DC coupling:

Fig.5 Positive side output voltage

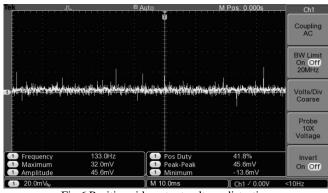

(2) Voltage distortion waveform at positive 15V side in AC coupling:

Fig.6 Positive side output voltage distortion

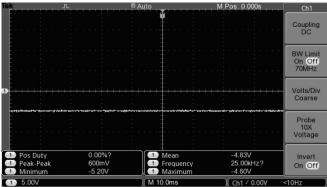

(3)Voltage Waveform Captured at negative 5V side in DC coupling:

Fig.7 Negative side output voltage

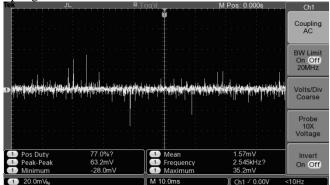

(4)Voltage distortion waveformat negative 5V side in AC coupling:

Fig.6 Negative side output voltage distortion

#### IJTRD|Mar-Apr2015 AvailableOnline@www.ijtrd.com

Fig.7 Hardware implementation of SMPS

### **IV. CONCLUSION**

In this paper, requirement of IGBT driver for an industrial drive application is presented. The main objective was to give mathematical results of the SMPS Circuit as well as the implementation of SMPS circuit which is required to generate the positive as well as negative voltage for the IGBT driver IC. Hardware results of SMPS are in line with the mathematical results.

### Acknowledgment

This research paper is made possible through the help and support from everyone. First and foremost, I would like to thank my guide Prof.P.N.kapil, Electrical Department, Institute of technology ,Nirma university for his most support, advice and encouragement. Second, I would like to thank Dr. P.N.Tekwani ,Head of Electrical Department , Institute of technology ,Nirma university.

# References

[1]Laurent Dulau, Serge Pontarollo, Anthony Boimond, Jean-François Garnier, Nicole Giraudo, and Olivier Terrasse, "A New Gate Driver Integrated Circuit for IGBT Devices With Advanced Protections", IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 21, NO. 1, JANUARY 2006.

[2]N.Rouger, J-C Crebier, R. Mitova, L. Aubard, C. Schaeffer, "Fully integrated driver power supply for insulated gate transistors", 18th International Symposium on Power Semiconductor Devices & IC's June 4-8, 2006 Naples, Italy.